Cadence 报错分析与解决方案指南

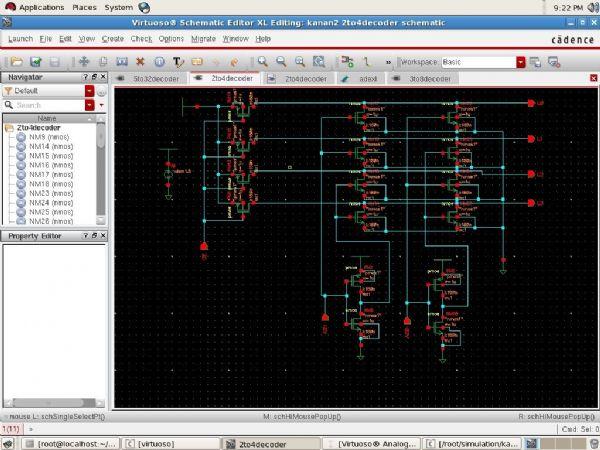

在电子设计自动化(EDA)领域,Cadence 软件套件被广泛应用于集成电路(IC)的设计、仿真和验证,在使用 Cadence 过程中,设计师可能会遇到各种错误或警告信息,这些通常被称为“报错”,本文旨在全面分析 Cadence 中常见的报错类型,提供逻辑清晰的诊断思路及解决方案,并通过表格形式归纳关键信息,最后附上常见问题的FAQs以供参考。

一、Cadence 常见报错类型及原因

| 报错编号 | 描述 | 可能原因 |

| 1 | 编译错误 (Compilation Error) | 语法错误、未定义变量、模块引用缺失等。 |

| 2 | 仿真错误 (Simulation Error) | 模型不匹配、初始条件设置不当、仿真时间步长不合理等。 |

| 3 | 布局问题 (Layout Issues) | DRC(Design Rule Check)违规、LVS(Layout Versus Schematic)不一致等。 |

| 4 | 时序违例 (Timing Violations) | 时钟域冲突、信号延迟超限、建立保持时间不足等。 |

| 5 | 电源完整性问题 (Power Integrity Issues) | IR Drop、电迁移、热效应导致的供电不稳定。 |

| 6 | 测试收敛性问题 (Test Convergence Issues) | 测试向量生成失败、覆盖率不足、仿真器资源限制等。 |

二、诊断思路与解决方案

1.编译错误

诊断:查看具体错误信息,定位到出错行或文件。

解决:修正语法错误,确保所有变量和模块都已定义且正确引用,使用Lint工具进行静态代码检查。

2.仿真错误

诊断:分析仿真日志,识别错误发生的时间和位置。

解决:检查模型文件是否正确加载,调整初始条件和仿真参数,如时间步长,以确保仿真稳定性。

3.布局问题

诊断:运行DRC和LVS检查,详细阅读报告。

解决:根据DRC报告调整布局以满足设计规则,对于LVS不一致,需回到原理图或修改布局直至匹配。

4.时序违例

诊断:利用静态时序分析(STA)工具识别关键路径上的违例。

解决:优化时钟树结构,调整缓冲器/反相器插入策略,重新布线减少延迟。

5.电源完整性问题

诊断:通过PI(Power Integrity)分析工具评估电压降和电流密度。

解决:增加电源轨宽度,添加去耦电容,优化供电网络设计以减小IR Drop和电迁移风险。

6.测试收敛性问题

诊断:审查测试计划和覆盖率报告,检查仿真资源分配。

解决:优化测试向量,提高故障模拟效率,考虑分布式仿真或硬件加速方案。

三、相关问答FAQs

Q1: 如何在 Cadence 中快速定位编译错误?

A1: 仔细阅读编译器输出的错误消息,它通常会指出错误的文件名和行号,使用文本编辑器或IDE直接跳转到指定位置,检查并修复语法错误、未声明的标识符或错误的模块调用,启用详细的编译选项可以帮助提供更多上下文信息,便于调试。

Q2: 如果遇到复杂的时序违例,如何有效解决?

A2: 面对复杂的时序问题,首先利用STA工具进行全面分析,识别出所有关键路径上的违例,针对每个违例,可以尝试以下步骤:

优化逻辑设计,减少不必要的逻辑级数。

调整时钟树结构,平衡时钟延迟。

在关键路径上插入缓冲器或反相器,以改善信号传播时间。

如果物理布局允许,重新布线减少互连延迟。

重新运行STA验证修改效果,必要时迭代上述过程直至满足时序要求。