PCB布线报错的常见原因与解决思路

在PCB设计过程中,布线环节是决定电路性能的关键步骤之一,许多工程师在实际操作中频繁遭遇“布线报错”问题,导致设计进度受阻,这些报错信息看似复杂,但往往源于一些基础设计规则或操作细节的疏漏,本文将结合常见错误场景,分析PCB布线报错的核心原因,并提供可行的优化策略。

一、设计规则冲突:从基础设置入手

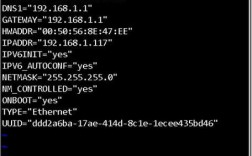

PCB设计软件(如Altium Designer、Cadence等)通常内置了设计规则检查(DRC)功能,用于确保布线符合生产要求,若布线时频繁报错,首先要检查DRC规则是否设置合理。

1、间距问题

导线与焊盘、过孔、其他导线之间的安全间距不足,是导致报错的典型原因,高压信号线与低压信号线未保持足够间距,可能触发短路风险警告,解决方法是根据电路特性调整规则库中的“Clearance”参数,或针对特定网络单独设置间距规则。

2、线宽与电流不匹配

电源线或大电流路径的线宽过窄,可能导致温升过高甚至烧毁,设计时需参考IPC标准中的线宽载流能力表,结合软件中的“Width规则”提前定义关键网络的线宽范围。

二、电气规则错误:关注信号完整性

布线报错有时并非物理连接问题,而是由信号完整性(SI)或电磁兼容性(EMC)规则引发。

1、未闭合的回路与天线效应

高频信号路径未设计合理的回流路径,可能形成天线效应,产生电磁干扰,此时软件可能提示“Unrouted Net”或“Stub Length”错误,对策包括:优化地平面完整性,缩短信号回流路径,避免出现悬空导线。

2、差分对布线失误

差分信号对(如USB、HDMI)的布线需严格保持等长、等距,若两条线长度差超过允许值,软件会提示“Differential Pair Length Mismatch”,可通过蛇形走线调整长度差,并锁定差分对属性以避免误操作。

三、网络连接问题:从原理图到PCB的映射

原理图与PCB之间的网络表不一致,是隐蔽却高频的报错诱因。

1、未正确导入网络标签

若原理图中的网络标签(Net Label)未正确传递至PCB,布线时会出现“Flying Net”错误,需检查原理图与PCB的同步状态,确保所有网络已完整关联。

2、元件封装不匹配

原理图符号与PCB封装的引脚定义不一致(如引脚编号错位),将导致网络连接错误,某芯片的1号脚在原理图中定义为电源输入,但在PCB封装中误接到地平面,此类问题需逐一核对封装库,必要时手动修正引脚映射关系。

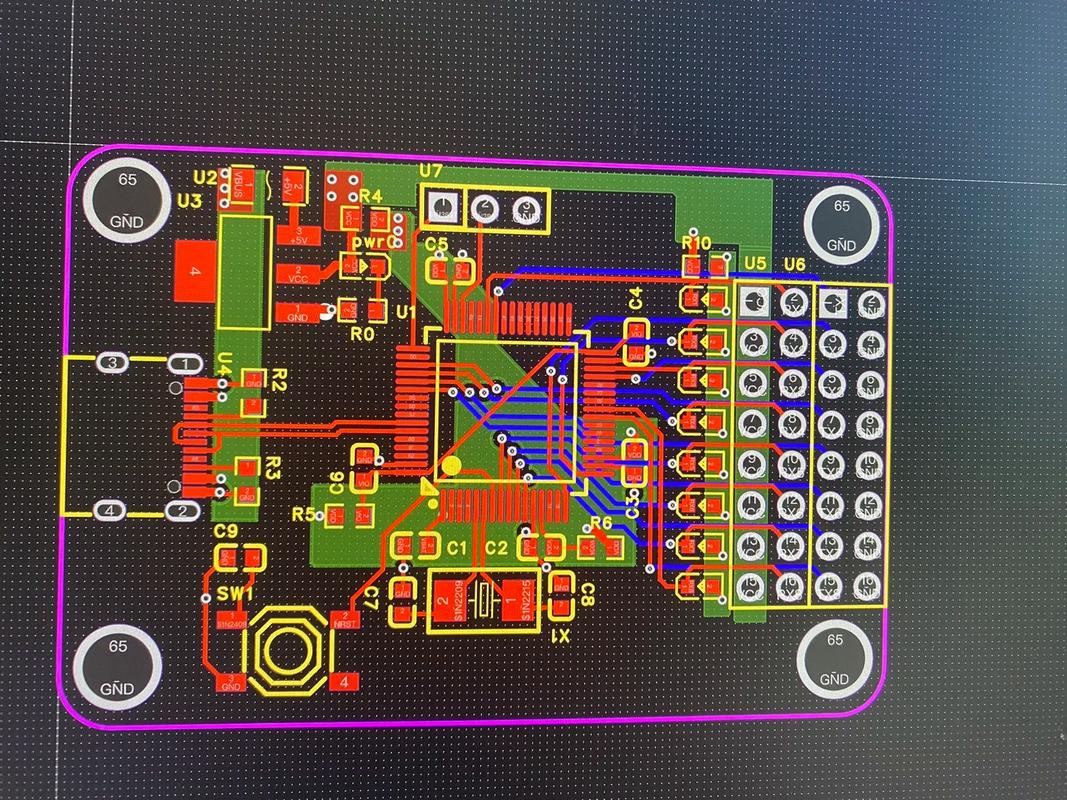

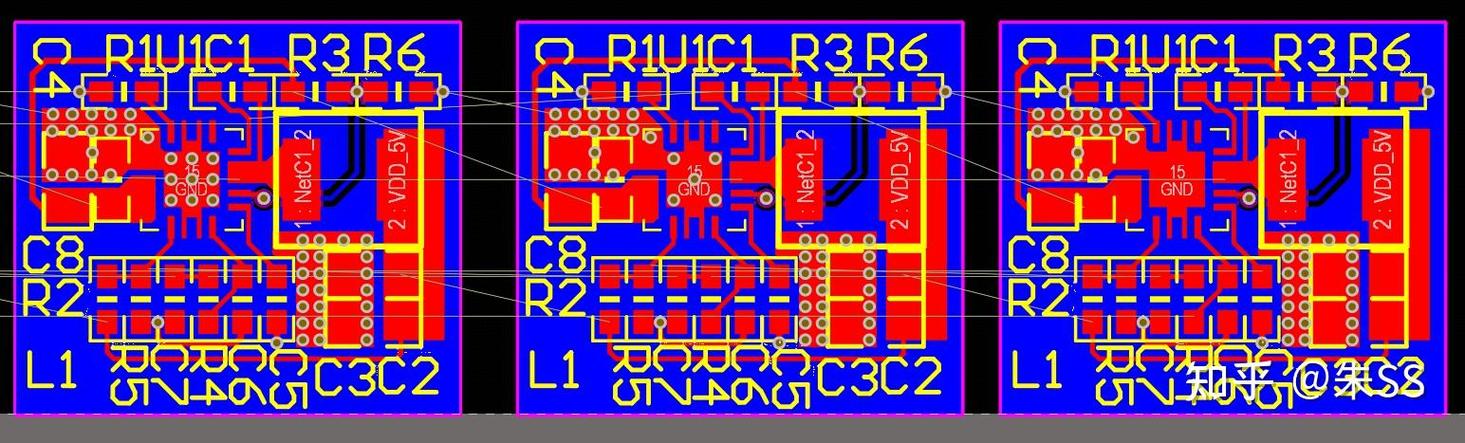

四、布局不合理:优化结构降低复杂度

PCB布局与布线紧密关联,若元件排布混乱,可能直接导致布线无法完成。

1、元件密度过高

高密度元件区域容易引发导线交叉、过孔堆积等问题,可通过分层策略解决:将电源与地线布置在内层,信号线布于表层;或采用“模块化布局”将功能区块分开,预留布线通道。

2、过孔使用不当

盲目增加过孔数量会导致制造成本上升,且可能违反生产商的工艺限制(如最小孔径要求),建议通过“Fanout”功能规划过孔位置,优先使用盲埋孔技术压缩空间。

**五、进阶优化:工具与经验结合

除基础规则外,合理利用设计工具的高级功能可显著提升布线成功率。

1、自动布线辅助与手动调整

完全依赖自动布线可能产生非最优路径,但手动逐条布线效率低下,推荐策略是:先通过自动布线完成简单网络,再手动优化关键路径(如时钟线、射频线)。

2、仿真验证提前介入

在布线完成后,使用信号完整性仿真工具(如HyperLynx)检查反射、串扰等问题,若仿真结果异常,需返回布线阶段调整拓扑结构或端接方式。

观点与建议

PCB布线报错本质上是设计规则与物理实现之间的冲突反馈,解决这类问题不能仅依赖“试错法”,而应从设计源头系统性优化:

规则先行:在项目初期明确工艺要求,定制DRC规则模板;

分层设计:将电源、信号、地平面分层处理,减少交叉干扰;

持续学习:关注行业标准更新(如IPC-2221),提升对高速、高密度电路的设计能力。

对于新手工程师,建议从简单板卡入手,逐步掌握规则配置与布线技巧;资深从业者则需关注新材料、新工艺(如高频板材、HDI技术)对布线的影响,只有将工具功能、设计经验与工程需求结合,才能从根本上降低报错频率,提升设计效率。