在电子设计自动化(EDA)过程中,铺铜是一个常见的操作,用于增强电路的电气性能和可靠性,在铺铜过程中经常会遇到DRC(设计规则检查)报错,尤其是与间距相关的问题,这些错误如果不妥善处理,可能导致电路板无法正常工作或制造困难。

铺铜报错原因分析

1、设计规则设置不当:

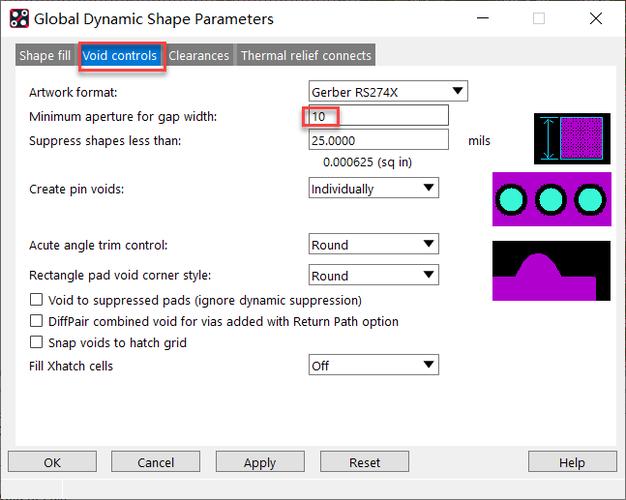

设计规则是EDA工具用来约束电路布局和布线的基本准则,如果这些规则设置不合理,例如最小间距、最小线宽等参数设置过小,就会导致铺铜后的DRC报错。

解决方法是仔细检查并调整设计规则,确保它们符合PCB制造商的要求以及电路设计的实际需求。

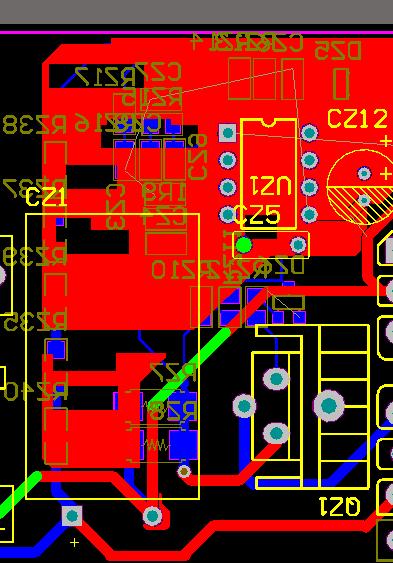

2、铜块布局问题:

即使设计规则设置正确,铜块的布局也可能导致DRC错误,铜块与其他电路元素(如焊盘、过孔、导线等)之间的距离可能不足。

解决这一问题的方法是通过手动调整铜块的位置或形状,或者修改其他电路元素的布局,以确保所有元素之间的间距满足设计规则的要求。

3、铜块属性设置不当:

铜块的属性,如线宽、线距等,也需要符合设计规则,如果这些属性设置不当,同样会导致DRC报错。

需要检查并修改铜块的属性设置,确保它们符合设计规则的要求。

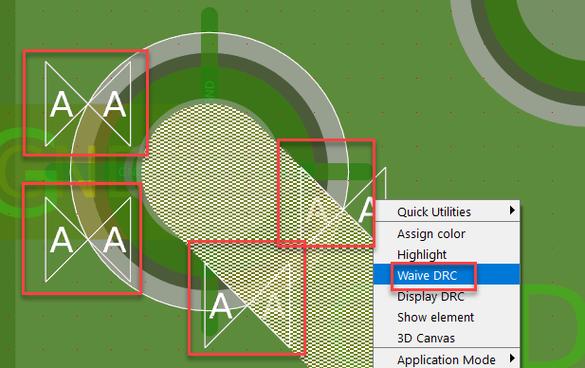

4、软件版本或BUG问题:

有时,DRC报错可能是由于使用的EDA软件版本过旧或存在BUG导致的。

尝试更新软件到最新版本,或者查看是否有针对该问题的补丁或解决方案。

5、自动修复功能:

一些高级EDA工具提供了自动修复功能,能够根据当前的设计规则自动调整布局以消除DRC错误。

可以尝试使用这一功能来快速解决问题。

6、咨询技术支持:

如果以上方法都无法解决问题,建议咨询EDA工具的技术支持人员获取帮助。

他们可以提供更专业的指导和解决方案。

铺铜报错距离报错的具体案例及解决方法

1、案例一:在立创EDA中铺铜后出现游离的铜块导致DRC报错。

解决方法:首先检查设计规则是否正确设置,特别是最小间距等参数;然后尝试调整铜块的布局或修改其属性;如果问题仍然存在,可以尝试重新铺铜或咨询技术支持。

2、案例二:在EDA中铺铜区域与其他电路元素(如过孔、焊盘等)之间的间距不足导致DRC报错。

解决方法:手动编辑铺铜形状或扩大其他元件焊盘、过孔周围的隔离环尺寸来增加它们之间的间距;同时检查并修改设计规则中的间距设置,确保它们符合实际需求。

相关问答FAQs

1、问题一:为什么铺铜后会出现游离的铜块?

解答:游离的铜块通常是由于设计规则设置不当或铜块布局不合理导致的,在铺铜过程中,如果某些区域的铜块没有与其他电路元素相连,就会形成游离的铜块,这会导致DRC报错,因为游离的铜块可能违反了设计规则中的最小面积或最小间距要求,为了解决这个问题,需要仔细检查设计规则和铜块布局,并进行调整。

2、问题二:如何避免铺铜后出现间距错误?

解答:为了避免铺铜后出现间距错误,需要在设计初期就仔细规划电路布局和布线策略,确保所有电路元素之间的间距都符合设计规则的要求,在铺铜过程中,可以使用EDA工具的自动检测功能来检查间距错误,并及时进行调整,还需要注意保持电路设计的简洁性和清晰性,避免过于复杂的布局和布线导致间距错误难以发现和解决。