在芯片设计流程中,DC综合作为连接RTL代码与物理实现的核心环节,其稳定性直接影响项目周期,当工具链弹出报错信息时,工程师需要像急诊科医生处理病患那样,快速定位问题根源,本文将解析三类典型报错场景,并提供可落地的排查方案。

一、约束文件引发的"多米诺效应"

某28nm工艺节点的图像处理芯片项目中,综合阶段频繁出现"invalid constraint syntax"提示,工程师发现时钟约束语句中的分号误写为中文标点,这种细节错误导致整个约束文件失效,更隐蔽的问题可能出现在跨模块约束冲突——当两个子模块分别定义不同的时钟频率却未设置伪路径约束,工具会误判时序关系。

验证约束有效性的正确姿势是分步加载,先执行check_timing命令验证时钟定义完整性,再用report_constraint -all_violators逐层检查约束冲突,资深工程师常备两份约束模板:基础版本包含工艺库参数与时钟树规范,扩展版本则根据具体设计添加特殊约束。

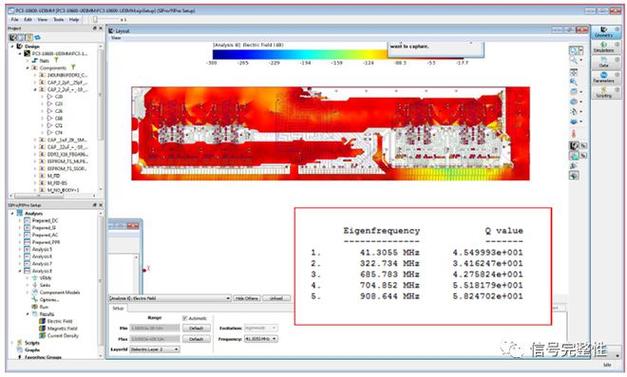

二、时序黑洞的探测技术

遇到"timing loop detected"报错时,新手工程师容易陷入无休止的迭代优化,某5G基带芯片案例显示,设计中的组合逻辑环路由三个异步FIFO控制模块构成,工具无法自动识别这种跨层次路径,此时需要手动插入set_disable_timing命令切断反馈回路,同时使用report_timing -loops生成环路拓扑图辅助分析。

对于建立时间违例,不能单纯依赖工具优化,某次AI加速器项目中,关键路径的违例量达0.3ns,通过group_path命令对特定路径组放宽约束后,时序虽闭合却导致功耗超标,最终采取寄存器重组方案:将64位累加器拆分为两个32位单元,用流水线技术平衡时序与面积。

三、资源争夺战的破局之道

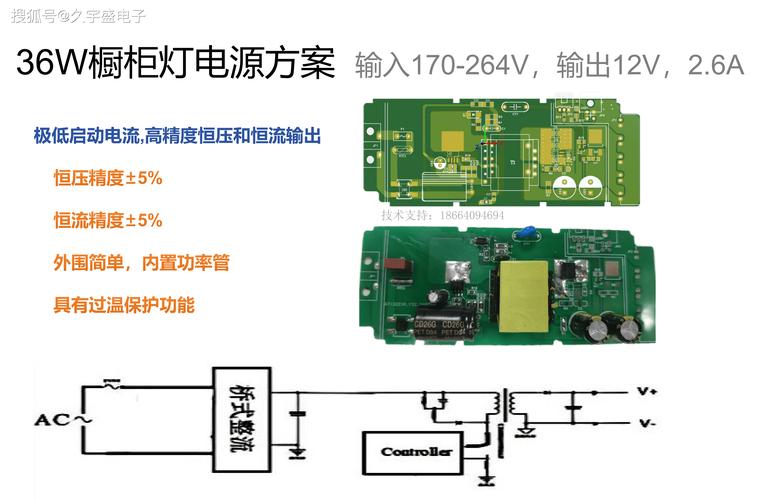

在40nm物联网芯片流片前一周,综合阶段突现"maximum transition time violated",查证发现电源管理模块的电压域配置错误,导致标准单元供电网络过载,这种问题无法通过常规优化解决,必须重新划分电源域并添加电平转换器。

存储器编译器的选择失误也曾让某团队付出惨痛代价,当使用28nm工艺的1R1W存储器实现双端口功能时,工具因无法识别混合端口配置而报错,改用经过工艺验证的2R2W编译器后,不仅消除报错,读写带宽还提升了40%。

四、环境配置的蝴蝶效应

某次跨国协作项目中,欧洲团队使用的DC 2020.03版本与国内团队的2021.12版本存在脚本兼容问题,导致同一份设计在两地产生不同综合结果,建立标准化环境需锁定三要素:工具版本号、工艺库日期标签、Tcl脚本校验码,推荐使用Docker容器封装综合环境,通过哈希值校验保证一致性。

当遇到"license checkout failed"报错时,切忌反复重试,某芯片公司曾因license服务器时区设置错误,导致凌晨时段的综合任务集体失败,完善的监控系统应包含license使用热力图,实时显示EDA工具的资源占用情况。

处理综合报错如同破解加密信息,每个错误代码都是设计缺陷的摩尔斯电码,资深工程师的竞争力不在于记住多少命令参数,而在于建立系统级思维框架——从RTL编码规范到物理实现约束,从工具特性到工艺演进,形成闭环验证体系,当警告信息再次闪烁时,不妨将其视为设计优化的路标,而非必须清除的障碍,这种认知转变,往往能带来意想不到的质量突破。