封装导入PCB报错?资深工程师的实用排查指南

作为一名从业多年的电子设计工程师,我深知将精心绘制的原理图封装顺利导入PCB设计环境是项目推进的关键一步。"封装导入报错"这个拦路虎,几乎每位硬件开发者都曾遭遇过,这类报错不仅打断工作流,其模糊的提示信息更令人头疼,我就结合常见案例和深层逻辑,分享系统性的排查与解决方案。

深入理解:封装到底是什么?

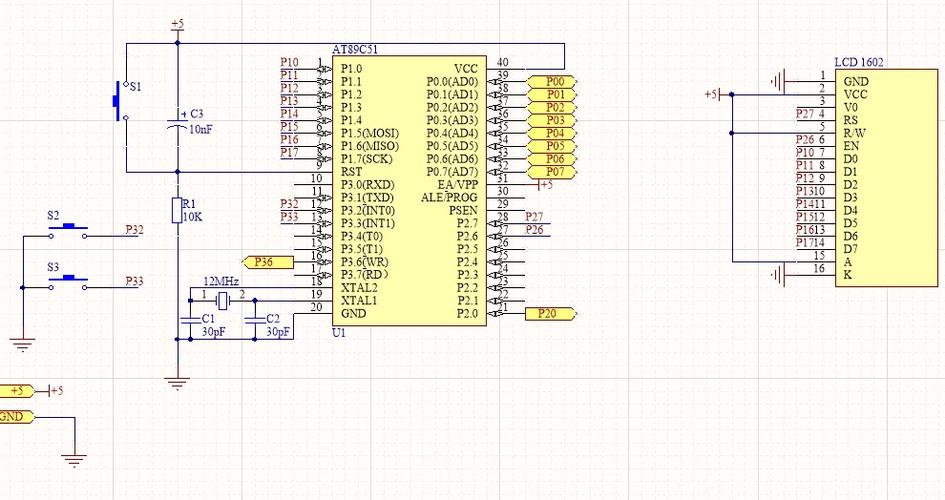

- 原理图符号 (Schematic Symbol): 你在原理图中看到的图形化表示,定义了元件的引脚功能和逻辑连接。

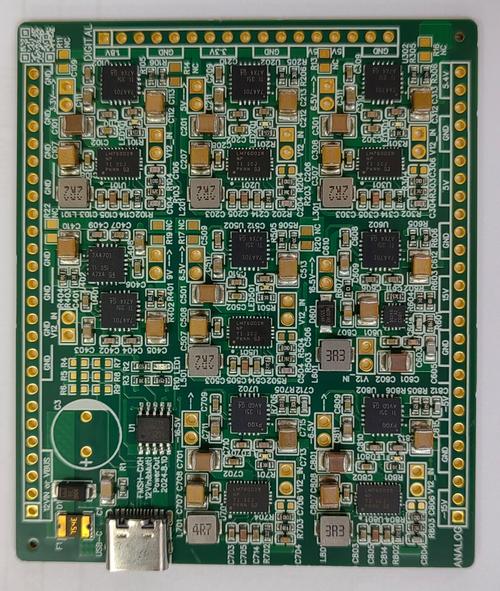

- PCB封装 (PCB Footprint/Land Pattern): 实物元件在PCB上的"落脚点",精确包含焊盘(Pads)的形状、尺寸、位置,以及元件外形轮廓(Silkscreen)、占位区域(Courtyard)、极性标识、参考编号位置等,它必须与元件的物理尺寸和引脚排列完全匹配。

- 模型关联: 原理图符号通过唯一的标识符(如库引用名)与对应的PCB封装绑定,导入报错的核心,往往就在于符号找不到、或无法正确匹配到它应该关联的封装。

高频报错场景与精准应对策略

"Footprint Not Found" 或 "Unknown Footprint"

- 核心原因: 设计软件在指定路径下找不到原理图符号关联的PCB封装文件。

- 彻底解决:

- 库路径验证: 首要检查PCB设计软件(如KiCad, Altium Designer, Cadence Allegro)的库搜索路径设置,确保包含目标封装的实际库文件(.PcbLib, .kicad_mod, .dra等)的文件夹路径已被准确添加且启用。一个常见陷阱: 库文件被移动或重命名,但软件路径未更新。

- 封装名精确核对: 在原理图编辑器中,双击元件属性,检查其"Footprint"字段名称,必须与目标库中PCB封装的确切名称(大小写敏感)完全一致,手动输入易出错,建议使用库浏览选择。

- 库完整性检查: 确认所需封装确实存在于已加载的库中,有时库文件可能损坏,尝试在库管理工具中重新加载或修复库。

"Pads Stack Not Found" 或 "Pad Size Error"

- 核心原因: 封装内的焊盘定义存在问题,或与当前PCB设计环境的层叠设置、设计规则冲突。

- 彻底解决:

- 封装内部审查: 打开报错封装库文件,仔细检查每个焊盘的定义:

- 各层(顶层、底层、内层、阻焊层Solder Mask、锡膏层Paste Mask)尺寸是否合理定义?尤其注意阻焊层通常比焊盘略大。

- 钻孔尺寸(Hole Size)是否设置?通孔元件必填。

- 焊盘编号(Pad Designator)是否与原理图符号引脚编号一一对应?

- 设计规则匹配: 检查PCB设计环境的默认设计规则(Design Rules),特别是最小焊盘尺寸、最小孔径等限制,新导入的封装焊盘/孔径若小于规则允许值,即会触发错误,需调整规则或修改封装。

- 封装内部审查: 打开报错封装库文件,仔细检查每个焊盘的定义:

"3D Model Not Found" 或 "3D Body Error" (常见于需要机械检查的设计)

- 核心原因: 封装关联的3D模型文件(如.STEP, .3DS)路径丢失、文件缺失或格式不兼容。

- 彻底解决:

- 3D模型路径检查: 确认软件设置中3D模型库的搜索路径包含模型文件所在位置。

- 模型文件验证: 检查文件是否存在,尝试用独立3D查看器打开,确保文件未损坏且格式受软件支持。

- 封装内关联修正: 在封装编辑器中,检查3D体(3D Body)属性,重新关联正确的模型文件或移除无效关联。

"Duplicate Pin Number" 或 "Pin Missing"

- 核心原因: 封装内部的焊盘编号出现重复,或原理图符号的引脚在封装中找不到对应编号的焊盘。

- 彻底解决:

- 封装焊盘编号审计: 在封装编辑器中,逐一检查所有焊盘的"Designator"属性,确保编号唯一且连续(如1, 2, 3...),无重复、无遗漏,特别注意多引脚连接器或IC。

- 原理图-封装映射验证: 仔细核对原理图符号的引脚编号列表与封装焊盘编号列表,必须完全一致,一个引脚编号在封装中找不到对应焊盘,或一个焊盘编号在符号中无对应引脚,都会导致映射失败。

"Invalid Shape" 或 "Graphical Error"

- 核心原因: 封装中的图形元素(如丝印线、铺铜区、禁布区)绘制不规范,存在极小线段、自相交多边形、非法顶点等几何错误。

- 彻底解决:

- 封装图形精修: 在封装编辑器中,放大检查所有线条、填充区域、多边形铺铜(如果有),使用软件的"检查"或"验证"功能(通常有DRC for Footprint选项),删除冗余的微小线段,确保所有轮廓闭合且无自相交,简化过于复杂的图形。

系统性排查流程:从混乱到清晰 遇到报错切忌盲目尝试,建议按此流程层层深入:

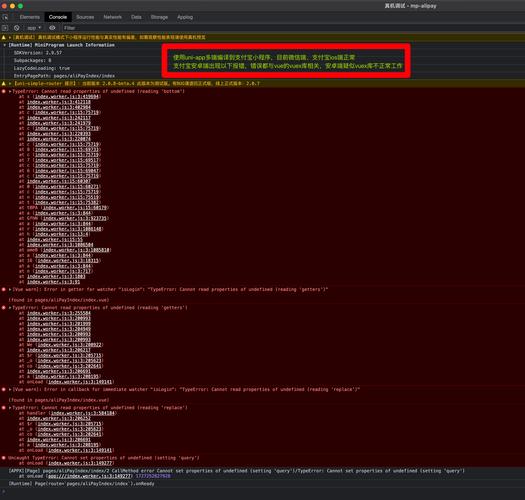

- 精读错误信息: 记录完整错误代码(如#701)和描述文本,这是最直接的线索。

- 锁定问题元件: 软件通常会高亮或列出报错元件/封装名,精准定位源头。

- 验证库与路径: 立即检查库管理设置和文件路径,这是基础。

- 审查封装定义: 打开报错封装文件,按上述高频错误点逐一检查焊盘、编号、图形。

- 核对原理图映射: 确保符号引脚与封装焊盘编号严丝合缝。

- 检查设计环境: 确认PCB设计规则未对封装尺寸构成限制。

- 善用工具验证: 运行封装库的DRC(设计规则检查)功能,它能自动捕捉许多潜在错误。

- 简化测试: 尝试在空白PCB文件中单独导入该封装,排除其他设计干扰。

防患于未然:建立稳健的封装管理

- 标准化建库: 制定并严格遵守内部封装命名规范、建库规则(焊盘命名、层定义、原点设置)。

- 中心库管理: 使用受控的公司级元件库,避免个人随意创建导致混乱。

- 源头数据优先: 尽可能从元件制造商官网下载权威的CAD封装数据(.STEP模型, .BRD, .DXF等)。

- 版本控制: 对重要库文件使用版本管理工具(如Git),追踪修改历史。

- 新封装必检: 创建或导入新封装后,务必在库编辑器中进行DRC检查,并在测试板上放置验证实际装配效果。

工程师视角:封装是硬件落地的基石 封装导入报错,表面是软件提示,深层次映射的是设计流程中的规范性与严谨性,一个微小的焊盘尺寸误差,可能导致贴片机无法精准焊接;一个错误的引脚映射,足以让整板功能瘫痪,与其在报错时焦头烂额,不如在源头——封装库的创建与管理上倾注更多心力,采用经过充分验证的、来自可靠来源的封装,建立严格的内部审核流程,是提升设计效率、保障产品质量的根本之道,每一次精准导入的背后,都是对物理世界电子连接的可靠承诺。

本文由资深电子工程师基于常见EDA工具(Altium/KiCad/Allegro等)实战经验撰写,旨在提供可操作的解决方案,文中案例及排查思路均源于真实项目场景。