在FPGA开发中,使用Questasim仿真工具时可能会遇到各种报错,这些错误可能源于多种原因,包括路径配置问题、端口声明问题、变量范围超出等,以下是一些常见的报错及其解决方法的汇总:

| 报错类型 | 描述 | 解决方法 |

找不到include文件 | 例如在reg_pkg.sv模块中引用param_def.v时出错。 | 在源代码中添加param_def.v的完整路径。 |

| Fatal error in Process MEMORY | 。 | 检查内存使用情况,确保没有内存溢出。 |

| 端口声明问题 | 提示检查未在顶层文件中修改的端口是否为wire。 | 确保所有未在顶层文件中修改的端口都被声明为wire。 |

| 变量范围超出 | ERROR: add_1 must be in range [1,DEPTH1]。 | 检查哪个变量的范围超出了限制,调整其范围。 |

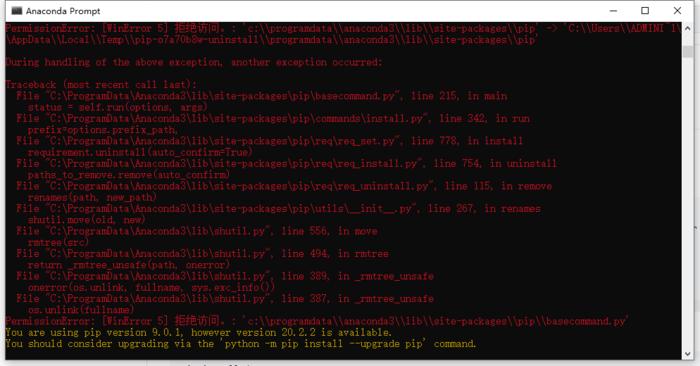

| 不带优化的仿真报错 | Error (suppressible): (vsim12110) All optimi ...。 | 尝试开启优化选项进行仿真。 |

FAQs

Q1: 如何解决找不到include文件的问题?

A1: 如果在仿真过程中遇到找不到include文件的问题,如在reg_pkg.sv模块中引用param_def.v时出错,可以在源代码中添加param_def.v的完整路径来解决这个问题。

Q2: 如果在使用Vivado调用Questasim(或Modelsim)时遇到“ERROR: add_1 must be in range [1,DEPTH1]”这样的报错,该如何解决?

A2: 这种报错通常是由于某个变量的范围超出了限制,解决方法是检查哪个变量的范围超出了限制,然后调整其范围,也可以检查Modelsim仿真中是否有哪个变量一直是红色的(X),或者是否有哪个IP核的输入一直是红色的(X),这可能有助于定位问题。