FPGA(现场可编程门阵列)是一种高度灵活的电子器件,广泛应用于硬件设计和原型开发中,在使用FPGA进行设计时,通常需要使用特定的软件工具进行综合、布局和布线等步骤,在这些过程中,可能会遇到各种报错信息,本文将详细探讨一种常见的FPGA报错——fpgamap错误,并提供全面的分析和解决方案。

一、什么是fpgamap 报错?

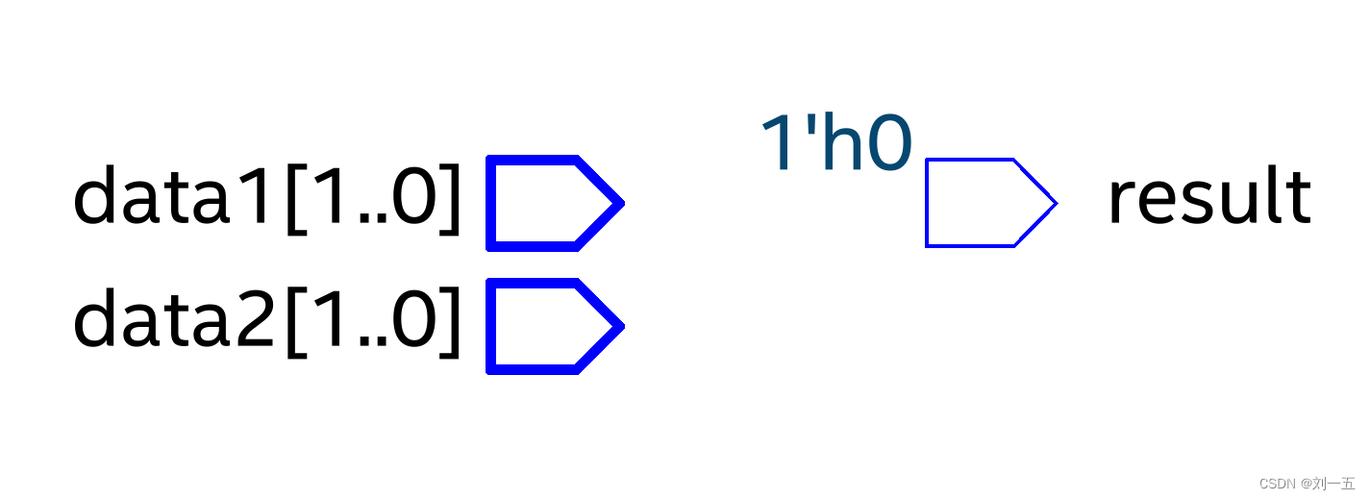

fpgamap 是 Xilinx ISE 工具集中的一个命令行工具,用于映射设计到特定 FPGA 设备上,在执行这个工具的过程中,如果遇到任何问题,它会生成一个或多个错误信息,这些报错信息通常会包含错误代码、错误描述以及可能的解决方案提示。

二、常见fpgamap 报错类型及原因分析

| 错误代码 | 错误描述 | 可能原因 |

| MAP_E | 映射阶段出现错误 | 逻辑设计中存在语法错误或不符合 FPGA 资源限制 |

| MAP_W | 映射阶段出现警告 | 逻辑设计中的某些部分可能存在潜在问题 |

| PLACE_E | 布局阶段出现错误 | 设计无法成功布局到目标 FPGA 上 |

| ROUTE_E | 布线阶段出现错误 | 设计无法成功布线到目标 FPGA 上 |

| TIMING_E | 时序分析阶段出现错误 | 设计的时序不满足要求 |

| DRC_E | 设计规则检查错误 | 设计违反了某些物理约束条件 |

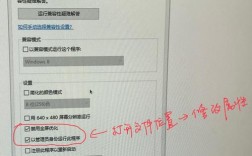

详细解决步骤

1、查看错误日志:仔细阅读错误日志文件,找到具体的错误代码和描述,这是解决问题的关键。

2、定位错误源:根据错误代码和描述,定位到具体的设计文件和代码行。

3、修正设计:根据错误提示,修改相应的设计文件,确保其符合 FPGA 的资源限制和设计规范。

4、重新运行fpgamap:修正后的设计需要重新运行fpgamap 以验证是否解决了问题。

5、多次迭代:如果仍然存在错误,重复上述步骤,直到所有错误都被解决。

示例分析

假设在执行fpgamap 时遇到了以下错误:

- Error: MAP_E: Partial mapping failed for LUT6_0 (.name CLB_X7Y10).

这个错误表明,在映射过程中,某个查找表(LUT)未能成功映射到目标位置,可能的原因是该位置的资源已经被其他逻辑占用,或者设计中的某个部分超出了该位置的资源限制。

解决方法:

1、检查设计:查看涉及的逻辑单元,确认是否存在资源竞争或过载的情况。

2、优化设计:尝试优化设计,减少资源占用,或者调整逻辑布局。

3、重新运行:修正后重新运行fpgamap,验证问题是否解决。

常见问题与解答 (FAQs)

Q1: 如何快速定位fpgamap 报错的具体位置?

A1: 查看错误日志文件中的错误代码和描述,它们通常会提供详细的错误信息和出错位置,可以使用 Xilinx ISE 提供的调试工具来进一步定位问题。

Q2: 如果fpgamap 报错提示资源不足,应该如何解决?

A2: 检查设计中是否存在资源浪费的情况,如不必要的逻辑重复,尝试优化设计,减少资源占用,如果必要,可以考虑升级到更高性能的 FPGA 设备。

通过以上分析和解答,希望能帮助大家更好地理解和解决fpgamap 报错问题,在实际设计过程中,遇到问题不要慌张,按照步骤逐步排查和解决,总能找到合适的解决方案。