在电子设计领域,Altium Designer作为一款功能强大的PCB设计工具,被广泛用于芯片封装、电路板布局等环节,用户在实际操作中难免会遇到各类报错提示,这不仅影响设计效率,还可能隐藏潜在的设计风险,本文将从常见报错类型入手,结合工程实践经验,为设计者提供系统性解决方案。

一、芯片封装类报错解析

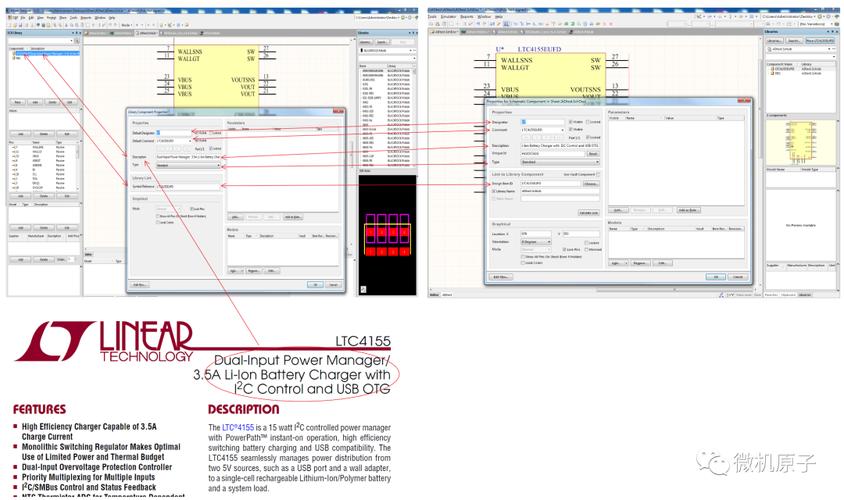

1. 引脚匹配异常

当原理图符号与PCB封装引脚数量不一致时,系统会触发"Pins do not match"错误,这类问题常因元件库管理混乱导致,建议通过以下步骤排查:

- 使用"Tools > Footprint Manager"工具对比原理图与封装引脚定义

- 检查焊盘编号是否与原理图引脚编号完全对应

- 确认是否存在隐藏引脚未正确设置

2. 3D模型冲突警告

出现"3D Body clashes"提示时,往往意味着元件实体模型存在空间重叠,此时应:

- 在3D视图模式下旋转检查元件位置

- 调整元件高度参数或修改封装设计

- 启用"View > 3D Layout"的碰撞检测功能进行预验证

3. 热焊盘连接错误

涉及散热焊盘的设计常出现"Unconnected Pin"警报,处理要点包括:

- 确认是否开启"Polygon Connect Style"中的热焊盘连接规则

- 检查焊盘与铜箔层的网络分配一致性

- 针对大电流器件设置独立的热焊盘连接规则

二、电气规则校验(ERC)典型问题

1. 悬浮网络警告

"Floating Net"类错误需优先排除设计疏忽:

- 检查未连接器件的使能引脚是否配置上拉/下拉电阻

- 验证未使用的芯片引脚是否已做安全处理

- 使用"PCB面板"的网络分析功能定位悬空节点

2. 电源短路风险

不同电压网络意外连接会导致"Short Circuit"报错,解决方法:

- 分层检查电源分配网络(PDN)走线

- 设置差异化的电源网络间距规则

- 在布局阶段使用颜色区分不同电压等级的网络

3. 信号完整性预警

高频设计中出现"Signal Length Mismatch"时,应:

- 启用差分对布线工具保证线长匹配

- 调整蛇形走线参数控制延时偏差

- 在规则设置中定义时序关键网络的误差范围

三、进阶问题处理策略

1. 元件库版本冲突

当多人协作时出现的"Library Out of Date"提示,建议建立:

- 标准化元件库管理流程

- 使用Altium Vault进行版本控制

- 定期执行库文件同步校验

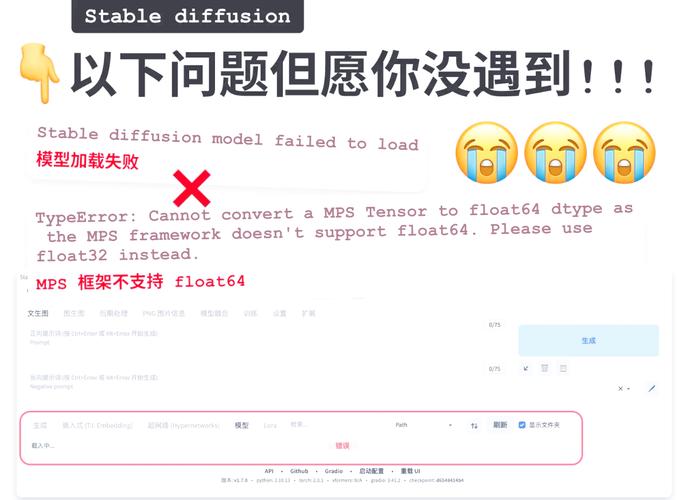

2. 制造规则(DRC)失效

突然出现的规则检查失效可尝试:

- 重置设计规则优先级顺序

- 检查是否存在规则例外设置

- 更新软件至最新版本修复潜在BUG

3. 工程文件损坏修复

面对"File Format Error"等严重错误时:

- 立即停止写入操作防止二次损坏

- 使用自动备份文件恢复(历史记录功能)

- 通过导入导出法重建工程架构

从项目实践经验看,90%的报错可通过规范设计流程避免,建议建立标准化的设计检查清单,在原理图阶段完成80%的潜在问题排查,对于复杂芯片设计,推荐采用模块化设计方法,将FPGA、MCU等核心器件单独建立子工程,定期清理设计缓存文件、维护统一的元件库、养成实时保存习惯,这些细节往往比处理报错本身更能提升设计效率。

设计工具的本质是辅助创意落地,报错信息实则是优化设计的指引,保持对每个警告提示的探究态度,逐步积累问题解决经验,才是驾驭EDA工具的关键,当遇到棘手问题时,合理利用Altium官方技术文档、开发者社区资源,往往能找到更优的解决路径。