在使用Multisim进行电路仿真时,许多用户会遇到“频率过高导致仿真报错”的问题,这种报错通常表现为仿真过程中软件提示“Time step too small”(时间步长过小)或“Simulation failed to converge”(仿真未收敛),这类问题不仅影响工作效率,还可能让初学者对仿真工具产生误解,本文将从技术原理、常见原因及解决方案三个维度展开分析,帮助用户快速定位并解决问题。

**一、仿真报错的技术背景

Multisim作为一款基于SPICE引擎的仿真软件,其核心原理是通过数值积分方法(如梯形法则、Gear算法)对电路微分方程进行迭代计算,当电路工作频率过高时,仿真器需要更小的时间步长来捕捉信号变化细节,时间步长过小会导致计算量指数级增长,超出软件预设的迭代次数或计算精度范围,最终触发报错机制。

举个简单例子:假设设计一个100MHz的振荡电路,仿真器可能需要在每个周期内采样至少100个点才能保证波形精度,若仿真总时长为1ms,则需处理10^5个数据点,这对计算机内存和处理器都是巨大挑战。

**二、高频报错的典型诱因

根据实际案例统计,高频仿真报错通常由以下四类原因导致:

1、电路参数设置不合理

- 信号源频率设置超出元件实际工作范围

- 电源上升/下降时间(Rise/Fall Time)未匹配高频需求

2、元件模型缺陷

- 高频电容/电感未启用高级模型(如Q因子、寄生参数)

- 晶体管模型缺少温度特性或频率响应参数

3、仿真配置冲突

- 最大时间步长(Maximum Time Step)设置过大

- 相对误差容限(Relative Tolerance)过于宽松

4、硬件资源瓶颈

- 计算机内存不足导致数据缓存溢出

- CPU单线程性能不足引发计算超时

**三、分步排查与解决方案

第一步:优化仿真参数

进入Simulate→Analyses and Simulation→Interactive Simulation Settings,重点调整以下参数:

- 将Maximum Time Step设置为信号周期的1/100~1/50(例如100MHz信号对应0.1ns~0.2ns)

- 将Relative Tolerance从默认0.001调整为0.0001以提高精度

- 勾选Use Gear integration method以增强高斜率信号的稳定性

第二步:校准元件模型

1、右键点击高频元件(如电感、晶体管),选择Properties→Value,确认已勾选Advanced选项

2、为关键元件添加寄生参数:

- 电感串联电阻(ESR)

- 电容等效串联电感(ESL)

3、通过Tools→Model Maker生成定制化IBIS/SPICE模型

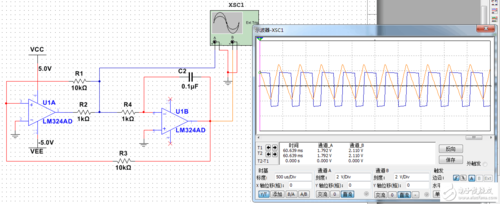

第三步:简化电路结构

- 对非关键路径的模块(如电源滤波网络)使用理想化模型替代

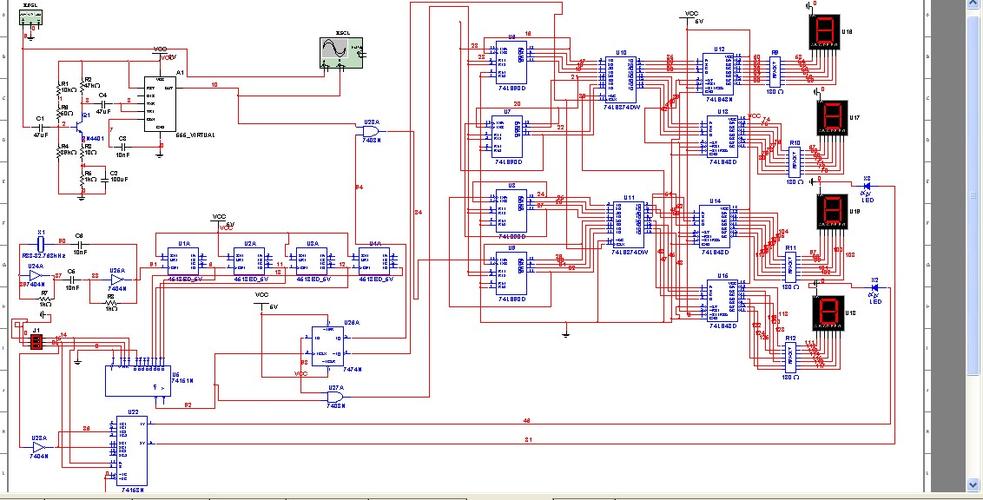

- 利用Hierarchical Block功能将大规模电路分块仿真

- 关闭波形图中非必要信号的实时显示以降低内存占用

第四步:硬件级优化

- 在Options→Global Preferences→Workspace中启用多线程加速(需处理器支持)

- 将虚拟内存页面文件大小调整为物理内存的1.5~2倍

- 对持续出现报错的复杂电路,可尝试导出网表文件(.cir)并在高性能服务器上运行

**四、典型案例解析

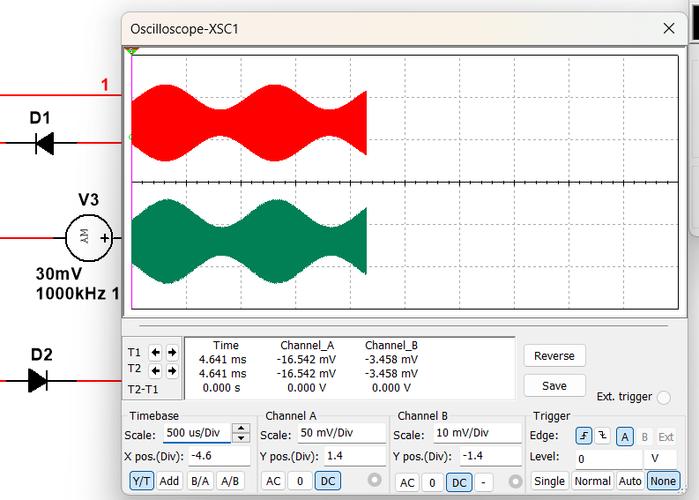

某射频放大器设计项目中,用户使用2SC3356晶体管搭建1.2GHz放大电路时频繁报错,经排查发现:

1、晶体管模型未包含封装寄生电感(约0.5nH),实际仿真频率被限制在800MHz以下

2、瞬态分析的最大时间步长保持默认值1μs,远高于所需精度

解决方案:

- 在元件属性中添加Lead Inductance(引脚电感)参数

- 将时间步长调整为0.05ns,并启用Gear算法

调整后仿真顺利完成,实测增益曲线与理论值误差小于3%。

**五、关于高频仿真的实践建议

1、分级验证原则:先对子模块进行低频验证,再逐步提升频率至目标值

2、模型优先策略:直接从器件厂商获取最新SPICE模型,避免使用通用库中的简化模型

3、资源分配技巧:关闭后台程序,通过任务管理器将Multisim进程优先级设为“高”

4、软件版本管理:NI Multisim 14.1之后的版本对高频仿真优化显著,建议升级至最新版

高频电路仿真是理论与实践的结合点,既需要理解数值计算的内在逻辑,也要掌握工具软件的操作细节,当报错发生时,系统化的排查思路往往比盲目调整参数更有效,对于长期从事高频设计的工程师,建议建立自己的“参数模板库”,将已验证的仿真配置保存为预设文件,这将大幅提升后续项目的调试效率。