PADS过孔报错?资深工程师的深度排障指南

作为PCB设计工程师,你是否曾在深夜加班时,被PADS突然弹出的过孔报错窗口瞬间惊醒?那刺眼的红色警示,仿佛在嘲笑你所有的设计努力,别担心,这种令人抓狂的经历,是每位资深工程师的必经之路,我们就来彻底拆解PADS过孔报错的根源,并提供切实可行的解决方案。

过孔报错的本质:设计规则在“说话”

PADS中的过孔报错绝非无故刁难,它的核心逻辑在于——你设计中的某个过孔或一组过孔,违反了预先设定的设计规则约束(Design Rule Constraints, DRC),这些规则是确保PCB可制造性、可靠性的基石,软件并非制造障碍,而是在你提交昂贵的制版费用前,替你拦截潜在的设计失误,理解这一点,是解决问题的第一步。

高频过孔报错场景与精准修复方案

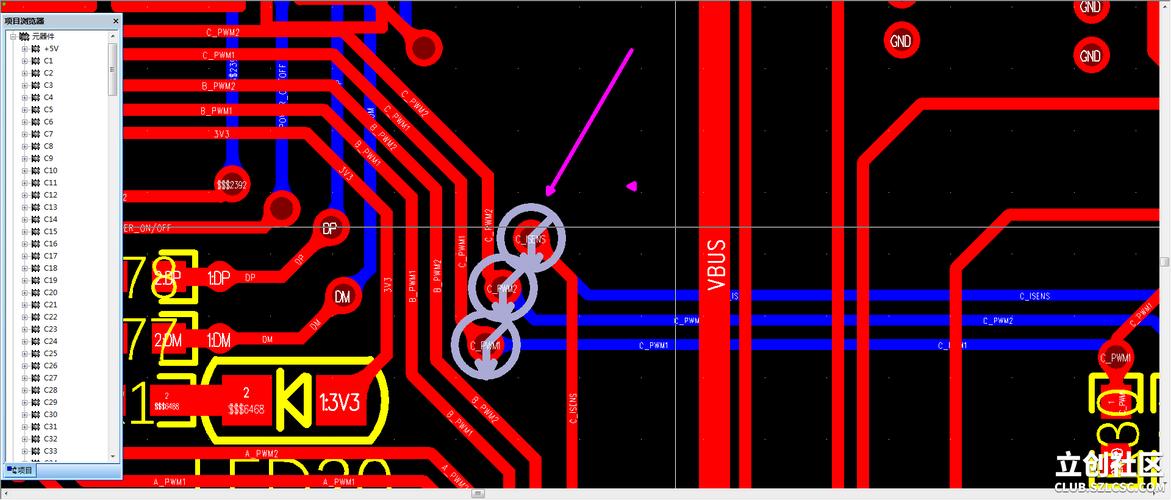

过孔与焊盘/走线的“亲密接触”

- 典型报错提示: “Clearance”、“Pad to Pad”、“Pad to Trace” 类错误最常见。

- 深度原因剖析:

- 过孔尺寸过大: 在密集区域,过孔直径(含焊环)超过了安全间距。

- 过孔放置位置不当: 过于靠近SMD焊盘、插件引脚、其他过孔或走线边缘。

- 规则设置偏差: 不同网络间(Net to Net)、相同网络内(Same Net)的安全间距规则未合理定义,特别是针对过孔的特殊规则(如Via to Via)。

- 工程师级修复策略:

- 精准测量与微调: 使用测量工具,严格检查过孔边缘到相邻导体边缘的实际距离,对照DRC规则数值进行精细位置调整。

- 优化过孔选型: 在满足电流承载和工艺能力前提下,优先选用更小尺寸的过孔(如8/16mil代替12/24mil),在PADS Router中启用“使用最小过孔”选项。

- 规则精细化管理: 进入

Setup -> Design Rules,重点检查:Clearance规则中不同网络、相同网络(Same Net)的间距设置。- 在

Net或Class规则中,是否单独定义了Via到其他对象的特殊间距(通常需更宽松)。 - 确认

Pad相关的间距规则(如Pad to Pad)是否合理。

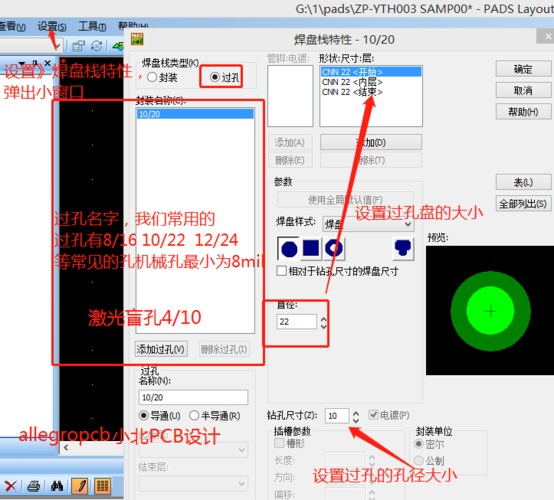

封装库中的“隐藏陷阱”

- 典型报错提示: 与特定器件关联的过孔报错,或涉及“Anti-Pad”(反焊盘)的错误。

- 深度原因剖析:

- 过孔焊盘定义错误: 库中该过孔类型的焊盘(Padstack)在各层的尺寸(Regular Pad)、热焊盘(Thermal Relief)、反焊盘(Anti-Pad)定义不当,Anti-Pad尺寸小于实际所需隔离区域,导致与平面层短路。

- 层定义不匹配: 过孔焊盘定义的层结构(起始层、结束层)与当前PCB板的实际层叠结构不一致。

- 工程师级修复策略:

- 彻底审查库元件: 在库管理器中,打开报错过孔对应的焊盘(Padstack),逐层检查:

Regular Pad(常规焊盘) 尺寸是否合理。Thermal Relief(热焊盘) 开口和内径是否满足焊接和电流需求。Anti-Pad(反焊盘/隔离盘) 尺寸是否足够大,确保在电源/地层能完全隔离过孔(通常比Drill Diameter大15-20mil以上)。

- 同步层叠结构: 确保PCB设计文件(

.pcb)的层叠结构(Setup -> Layer Definition)与过孔焊盘中定义的起始/结束层完全一致,不一致时需修改焊盘定义或调整板层设置。

- 彻底审查库元件: 在库管理器中,打开报错过孔对应的焊盘(Padstack),逐层检查:

网络属性与层限制的“无形束缚”

- 典型报错提示: “Unrouted Net”、“Stub”、“Layer Violation”等。

- 深度原因剖析:

- 布线层限制: 过孔连接的网络被错误地限制在特定布线层,而该过孔试图连接被禁止的层。

- 未完成布线: 过孔是布线的一部分,但该网络尚未完成布线(飞线仍存在)。

- 悬空过孔 (Stub): 过孔一端连接走线,另一端未连接任何有意义网络(尤其在高速设计中需避免)。

- 工程师级修复策略:

- 检查网络布线属性: 右键点击报错网络,选择

Properties->Routing,确认Layers选项卡下允许布线的层是否正确勾选,未被错误限制,检查Via选择是否被限制。 - 完成布线连接: 使用布线工具(

F3或图标),确保该过孔所在网络的所有飞线都被正确连接至目标焊盘。 - 清除无效过孔: 使用

Tools -> PadStacks -> Unused或Verify Design中的Stub检查项,定位并删除无任何连接关系的冗余过孔,对于高速设计中的Stub,考虑使用背钻(Backdrill)工艺或调整叠层设计。

- 检查网络布线属性: 右键点击报错网络,选择

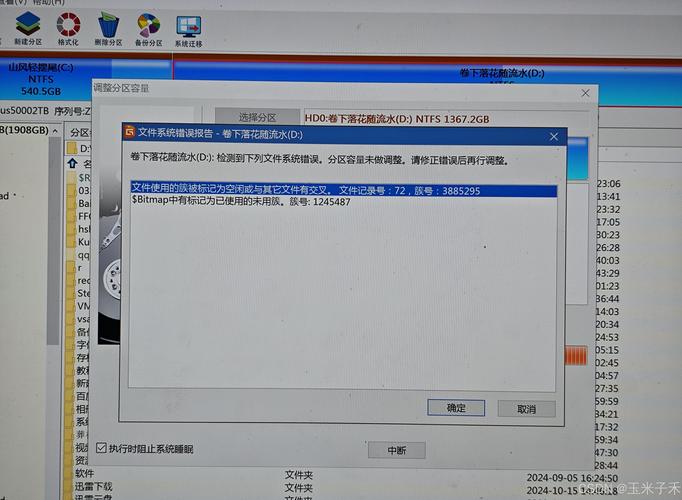

设计规则检查(DRC)的“执行盲区”

- 问题现象: 明显有间距问题却未报错,或报错位置不准确。

- 深度原因剖析:

- DRC未开启或未更新: 实时DRC(

Tools -> Options -> Design -> On-line DRC)被关闭,或修改设计/规则后未执行批量DRC(Tools -> Verify Design)。 - 规则优先级冲突: 更精细规则(如Class规则、Net规则)被更宽泛的默认规则覆盖。

- DRC未开启或未更新: 实时DRC(

- 工程师级修复策略:

- 强制启用实时DRC: 确保

On-line DRC设置为Prevent Errors(最严格)或Warn Errors,养成修改后随手按Ctrl+D刷新显示的习惯。 - 执行全面设计验证: 任何重大修改后,务必运行

Tools -> Verify Design,勾选所有相关检查项(Clearance、Connectivity、High Speed等),仔细查看报告并定位错误。 - 理清规则优先级: 在

Design Rules中,理解规则应用的优先级顺序(通常是Net > Class > Group > Layer > Default),确保特殊规则生效范围正确,未被默认规则覆盖,善用Rule Report功能分析。

- 强制启用实时DRC: 确保

观点:一次过孔报错的解决,远不止于点击几下鼠标,它是对设计规范严谨性的检验,对工艺理解深度的考察,更是工程师专业素养的体现,忽视这些看似微小的错误提示,往往意味着后期高昂的返工成本与潜在的质量风险,将每一次DRC报错视为优化设计的契机,你的PCB作品才能真正兼具功能与可靠性之美。