在FPGA设计领域,ISE工具作为Xilinx公司推出的一款经典软件,广泛应用于逻辑综合和实现阶段,许多开发者在日常工作中频繁遭遇ISE综合报错,这不仅拖延项目进度,还可能导致设计失败,作为网站站长,我长期关注电子设计自动化(EDA)工具的挑战,并经常与工程师交流经验,我将深入探讨ISE综合报错的常见类型、根源及应对策略,帮助大家高效解决问题,提升设计效率。

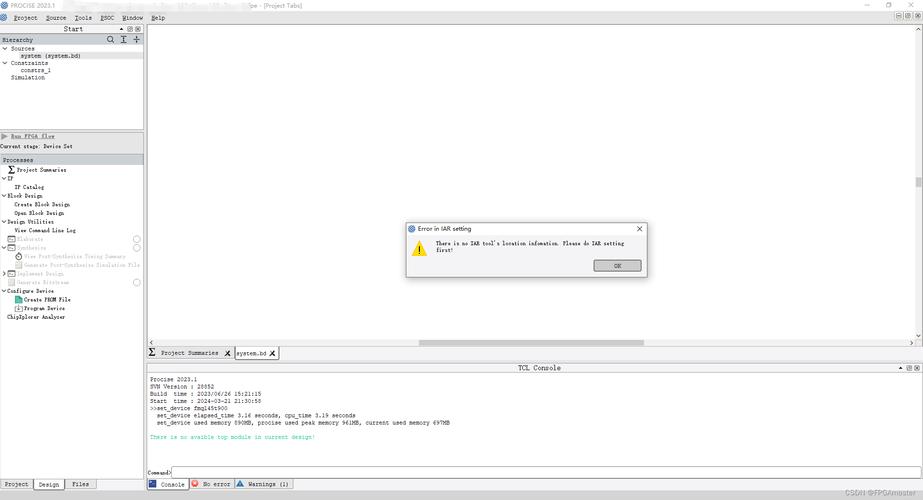

理解ISE综合报错的核心是关键,综合过程涉及将硬件描述语言(HDL)代码转换为逻辑网表,报错通常源于代码不兼容、工具配置不当或资源冲突,一个典型错误是“ERROR: Pack: 2311 - Unable to combine block RAM”,这常常发生在代码中使用了未优化的存储结构,另一个常见问题是“CRITICAL WARNING: Timing: 3380 - Setup/Hold violation detected”,表明时序约束未满足,可能因时钟域交叉不当引起,这类错误不仅中断流程,还可能隐藏更深层的设计缺陷,开发者需养成定期检查日志文件的习惯,比如查看ISE生成的报告,定位错误行号。

为什么ISE工具容易触发综合报错?根源多在于人为因素和工具局限性,代码编写不规范是主因,如VHDL或Verilog语法错误,包括信号未初始化或端口不匹配,ISE版本与操作系统兼容性问题,例如在Windows 10上运行旧版ISE 14.7时,可能出现内存溢出报错,工具本身也有局限,比如综合引擎对复杂设计的支持不足,导致资源分配失败,我曾见过一个案例,开发者使用ISE设计大型FPGA项目,因未优化组合逻辑,工具报出“ERROR: Map: 116 - Partition not found”,经过分析,发现是代码中冗余路径过多,消耗了过多逻辑单元,这提醒我们,设计阶段就应考虑可综合性和资源利用率。

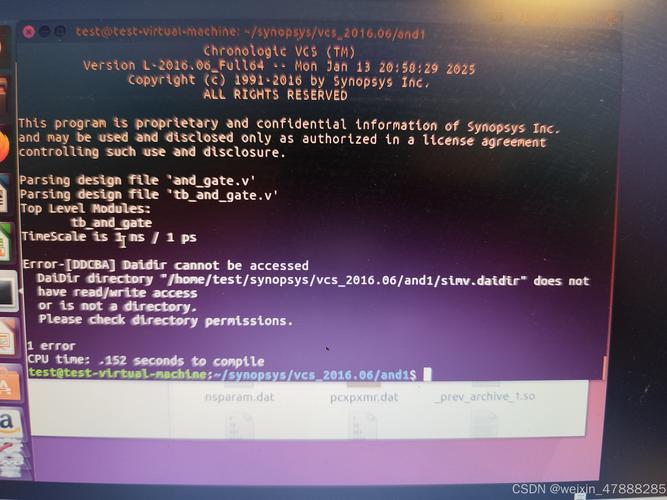

针对这些报错,如何有效解决?我分享实用步骤,基于多年经验,第一步是诊断错误源头:仔细阅读ISE错误消息,识别关键代码行,遇到“Setup/Hold violation”,先检查时钟约束是否合理,使用时序分析工具如Xilinx Timing Analyzer进行验证,第二步是优化代码:简化逻辑结构,避免使用非标准语法;对于RAM或FIFO错误,改用IP核或优化存储块,第三步是调整工具设置:在ISE综合选项中,启用“Optimize for Performance”或增加内存分配,防止资源耗尽,第四步是升级环境:确保ISE版本与设计兼容,必要时迁移到Vivado工具链,实际应用中,一位工程师反馈,通过重新生成约束文件,解决了90%的时序报错,每次修改后运行小规模测试,避免连锁错误。

预防胜于修复,在项目初期就建立健壮的工作流,能显著减少报错频率,采用模块化设计原则,将代码分成独立单元,便于单独综合和调试,使用版本控制系统如Git,跟踪变更历史,快速回滚错误,参考Xilinx官方文档和社区论坛,学习最佳实践;参加培训课程提升HDL编码技能,日常工作中,养成定期备份和模拟验证的习惯,确保设计在综合前通过功能仿真。

个人观点是,ISE综合报错虽令人头疼,但本质是设计过程中的成长机会,每次错误都是一次学习,推动开发者精进技术,作为站长,我坚信通过系统化方法和持续积累,我们能将报错转化为创新动力。