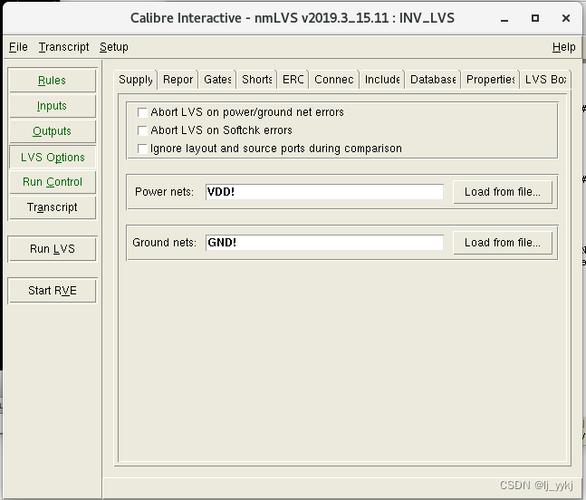

在Virtuoso中进行LVS(Layout Versus Schematic)验证时,可能会遇到各种报错,以下是一些常见的报错及其可能的原因和解决方法:

1、Netlist generation failed:

原因:在生成网表时出现错误,可能是由于原理图中存在未连接的节点或元件。

解决方法:检查原理图,确保所有元件都已正确连接,没有悬空的节点,可以尝试逐层检查并保存原理图。

2、Cannot find switch master cell for instance:

原因:在运行LVS时,找不到某个开关元件的主单元。

解决方法:检查工艺库是否正确加载,以及CDS_Netlist_Mode环境变量是否设置为Analog。

3、Licensing Error:

原因:软件许可问题,可能是虚拟机的虚拟网卡地址发生变化导致。

解决方法:修改license文件中的网卡地址,使其与当前系统的网卡地址匹配。

4、Compilation Error while compiling rules file:

原因:在提取版图参数时,编译规则文件出错。

解决方法:检查厂家提供的工艺库路径是否正确,并根据实际路径修改相关配置文件。

5、Fatal Error during Calibre View generation:

原因:在生成Calibre视图时发生致命错误。

解决方法:尝试添加环境变量CALIBRE_ENABLE_SKILL_PEXBA_MODE=1,并重启虚拟机。

6、The following products could not be licensed sufficiently:

原因:某些产品未能获得足够的许可。

解决方法:确保所有需要的软件许可都已正确安装和配置,特别是对于虚拟化环境,可能需要调整许可服务器的配置。

7、Error during netlisting of design:

原因:在设计网表化过程中出现错误。

解决方法:重新生成网表,并检查是否有任何未定义或错误的元件属性。

8、Error putprop: first arg must be either symbol, list, defstruct or user type:

原因:在设置属性时,第一个参数类型不正确。

解决方法:检查代码或脚本,确保传递给putprop函数的第一个参数是正确的类型。

9、Error while compiling rules file:

原因:在编译规则文件时出现错误。

解决方法:检查规则文件的语法和逻辑错误,确保所有引用的文件和路径都是正确的。

10、Error in connecting ports and nets:

原因:端口和网络之间的连接存在问题。

解决方法:检查端口和网络的定义,确保它们之间的连接是正确的。

11、Error in running simulations:

原因:在运行仿真时出现错误,可能是由于变量或参数不一致。

解决方法:同步提交点与活动设置中的变量和参数,然后重新运行仿真。

在进行LVS验证时,还需要注意以下几点:

确保使用的工具链(如Cadence Virtuoso、Calibre等)版本兼容。

定期更新和维护工艺库,以确保其与当前的设计流程相匹配。

在进行复杂的电路设计时,建议使用模块化设计方法,将大电路分解为小模块,分别进行设计和验证。

在设计过程中,经常保存工作进度,以防止意外的数据丢失。

以下是两个关于virtuosolvs报错的常见问题及其解答:

Q1: 为什么在进行LVS验证时会出现“Netlist generation failed”的错误?

A1: “Netlist generation failed”通常是因为在生成网表的过程中遇到了问题,这可能是由于原理图中存在未连接的节点或元件导致的,为了解决这个问题,你需要检查原理图,确保所有的元件都已正确连接,并且没有悬空的节点,你可以尝试逐层检查并保存原理图,以帮助定位问题所在。

Q2: 在进行LVS验证时,如果遇到“Cannot find switch master cell for instance”的错误应该怎么办?

A2: 这个错误通常意味着在运行LVS时,系统找不到某个开关元件的主单元,这可能是由于工艺库没有正确加载或者CDS_Netlist_Mode环境变量设置不正确导致的,为了解决这个问题,你需要检查工艺库是否正确加载,并确保CDS_Netlist_Mode环境变量被设置为Analog,如果问题仍然存在,你可能需要重新配置你的工作环境或联系技术支持以获取帮助。

通过以上步骤和方法,可以有效地解决Virtuoso LVS验证中的常见报错问题,提高电路设计的质量和可靠性。